最近在学习基于DE10-Nano的FPGA程序设计,这个过程有相对比较复杂的环境配置和一些容易犯的错误,在这里记录一下

环境的配置与操作流程

DE10-Nano所使用的FPGA的编号为Cyclone V 5CSEBA6U23I7,在配置Quartus的时候可以方便一点- 包含有仿真的项目,首先指定仿真工具使用

ModelSim;在主程序基本完成后(记得编译),自动生成TestBranch脚本;最后将其加入到仿真设定中 - 每次编译后都要重新生成

TestBranch,所以建议改一下文件名 - 每一次不同的配置前注意是否放入SD卡以及拨码开关的位置情况

- 对于HPS中的的文件传输,我们可以使用

rz -Z的方式实现文件传输 - 如果希望使用HPS来刷写FPGA,那么分以下几步

- 调节所有拨码开关到打开

- 向FAT分支中添加

rbf文件,命名为soc_system.rbf

- 由于

GLIBC的版本问题,所有的C程序应当放在DE10-Nano上编译

HPS编写注意

- 对于输入输出的部分至少要有两个连接在AMM上,否则会因为内存地址只有1而出错

Verilog编写注意

- 不能在不同的

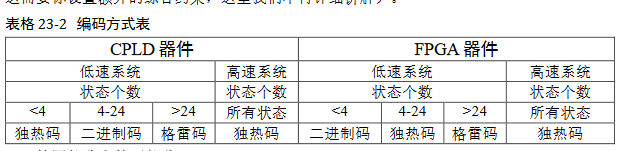

always块中对同一个变量修改 - 对于不同状态进行编码时,可以参考这张表

- 非阻塞复制的操作计算是在时钟边沿到来之前的值

- 如果一个

always块对某个寄存器赋值,而另外一个always块判断这个寄存器的值,那么这个值对应于时钟沿到来前的值(类似于非阻塞赋值)此时需要正确使用非阻塞赋值,避免出现冲突

- 在时序逻辑中,使用非阻塞赋值

- 注意在按钮摁下的过程会有非常多的时钟周期

例如每次摁下按钮,将某一个量加一,这个时候有两种解决方案,一个是使用按钮的上升沿触发,另外一种是使用系统时钟,处理按钮按下事件是否为第一次触发

- 例如复位”高电平触发”,是指当信号为高电平时,会发生复位

- 在编写Soc系统中时,需要注意

output是接口输出,从内存到FPGA(方向别搞错) - 在编写模块时的参数都是

wire

ModelSim使用注意

- 为了和系统时钟相匹配,需要记得修改时间尺度

TestBranch的always块中**记得把@allvec删去,否则无法仿真